1.5 Системный контроллер ВК28

4.1 Арифметические сумматоры

Сумматоры выполняют микрооперацию сложения слов. При сложении выполняется операция арифметического суммирования и дополнительные операции (учёт знаков, порядок слагаемых и др.). Указанные операции выполняются в арифметико-логических устройствах (АЛУ), ядром которых являются сумматоры.

Классификация сумматоров показана на рисунке 4.1. По числу входов различают полусумматоры, одноразрядные сумматоры (ОС) и многоразрядные сумматоры. Многоразрядные сумматоры делятся на последовательные, в которых обработка данных ведётся поочерёдно разряд за разрядом на одном и том же оборудовании, и параллельные, в которых слагаемые обрабатываются одновременно по всем разрядам и для каждого разряда имеется своё оборудование.

По способу организации межразрядных переносов параллельные сумматоры подразделяются на схемы с последовательным, параллельным переносами и с групповой структурой. В последних разрядная сетка разделена на поля, обрабатываемые группами разрядных схем. В группах и между ними могут применяться разные способы переносов, причем в наименованиях сумматоров вначале указывается вид переноса внутри группы. Например, термин «параллельный сумматор с параллельно-параллельным переносом» указывает па сумматор групповой структуры, в котором в группах и между ними осуществлен параллельный перенос. К комбинационным относят сумматоры, являющиеся комбинационными цепями в общепринятом смысле слова. Накапливающие сумматоры имеют память, в которой аккумулируют результаты суммирования так, что очередное слагаемое добавляется к результату, содержавшемуся в регистре-аккумуляторе.

Рисунок 4.1 – Классификация арифметических сумматоров

По способу трактирования различают синхронные и асинхронные сумматоры. Синхронные сумматоры имеют постоянное время, отводимое для суммирования независимо от значений слагаемых, в асинхронных вырабатывается признак завершения операции, при этом среднее время суммирования уменьшается, поскольку оно существенно меньше максимального. В зависимости от системы счисления различают двоичные, двоично-десятичные и другие сумматоры.

literaturki.net

1.5 Системный контроллер ВК28

- Подробности

- Категория: Микропроцессоры / микрокрнтроллеры

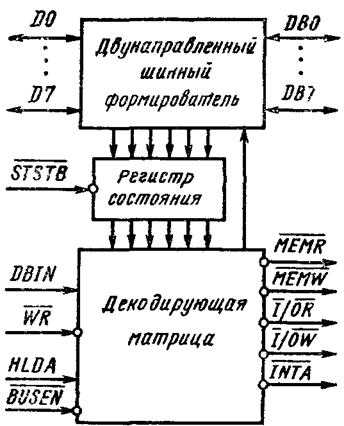

Системные контроллеры КР580ВК28 и КР580ВК38

Микросхемы КР580ВК28 и КР580ВК38 выполняют функции системного контроллера и шинного формирователя, осуществляют формирование управляющих сигналов обращения к ОЗУ или к устройствам ввода/вывода (УВВ) и обеспечивают прием и передачу 8-разрядной информации между шиной данных микропроцессора и системной шиной.

Отличие микросхемы КР580ВК28 от микросхемы КР580ВК38 состоит в формировании сигналов , . Микросхема КР580ВК28 формирует эти сигналы относительно сигнала «Запись», а микросхема КР580ВК38 — относительно сигнала

Риcунок 1.13 — Структурная схема КР580ВК28 и КР580ВК38

Таблица 1.3

| Номер вывода | Обозначение | Назначение |

| 6, 8, 10, 12,

15 17, 19, 21 |

D0-D7 | Шина данных |

| 5, 7, 9, 11,

13, 16, 18, 20 |

DB0-DB7 | Системная шина |

| 1 | Строб состояния | |

| 2 | HLDA | Подтверждение захвата |

| 3 | Запись | |

| 4 | DBIN | Прием |

| 11 | GND | Общий |

| 22 | Управление системной шиной | |

| 23 | Подтверждение прерывания | |

| 24 | MFMR | Чтение памяти |

| 25 | I/OR | Чтение УВВ |

| 26 | Запись в память | |

| 27 | Запись в УВВ | |

| 28 | Ucc | +5 В |

Регистр состояния выполнен на шести D-триггерах и предназначен для хранения информации о состоянии микропроцессора, поступающей по шине данных D0 — D7 Запись в регистр состояния осуществляется по сигналу , поступающему в начале каждого машинного цикла.

Декодирующая матрица в зависимости от режима работы микропроцессора, зафиксированного в регистре состояния, и входных управляющих сигналов HLDA, , DBIN формирует сигнал «Подтверждение прерывания» или сигналы чтения/записи при обращении к ОЗУ или УВВ. Назначение выводов микросхем КР580ВК28 и КР580ВК38 приведено в табл. 1.3.

Микросхемы КР580ВК28 и КР580ВК38

Дешифратор управляющих сигналов формирует один из управляющих сигналов в каждом машинном цикле: при чтении ЗУ — RD, при записи в ЗУ — WR, при чтении из УВВ — RD10, при записи в УВВ — WR10, при подтверждении запроса прерывания — сигнал 1NTA. Асинхронный сигнал BUSENуправляет выдачей данных с буферной схемы и управляющих сигналов с дешифратора: при напряжении низкого уровня на входе BUSENбуферная схема передает данные и формируется один из управляющих сигналов; при напряжение высокого уровня все выходы микросхемы переводятся в высокоомное состояние Напряжение высокого уровня на входе HLDAпереводит выходы ~RD, RD10, INTAв пассивное состояние (напряжение высокого уровня) и блокирует передачу информации через буферную схему данных. Управляющие сигналы WRи WR10 формируются в цикле записи в микросхеме КР580ВК28 по сигналу TR, в микросхеме КР580ВК38 — по сигналу STBПри работе с микропроцессором КР580ВМ80А системный контроллер в цикле подтверждения запроса прерывания формирует три сигнала INTAдля приема трех байтов команды CALLот контроллера прерывания КР580ВН59.

В небольших микропроцессорных смете мах выход INTAмикросхем КР580ВК28/КР580ВК38 можно подсоединить к напряжению + 12 В через резистор сопротивлением 1 кОм. Во время действия сигнала RCбуферная схема данных микросхемы формирует код команды RST7 и передает на канал данных микропроцессора. Таким образом, микро схема обеспечивает единственный вектор прерывания с номером 7 без дополнительных компонентов. |

dplm2008.narod.ru